HP 520 5/XX User Manual Page 73

- Page / 146

- Table of contents

- BOOKMARKS

Rated. / 5. Based on customer reviews

73

3 System Board (P/Ns D3657-63001 and D3661-63001)

Devices on the Processor Local Bus

The computer will execute erratically, if at all, if the configuration switches

are set to operate at a higher processor speed than the processor is capable

of supporting. This may cause damage to the PC.

Setting the switches to operate at a slower speed than the processor is

capable of supporting would not cause any failure of operation but would

cause instructions to be executed more slowly than they should be.

Cache Memory

The PC allows for the provision of two levels of cache memory:

• Level-one cache memory which is fabricated by Intel in the Pentium

processor chip

• Level-two cache memory is optionally installed as a memory module on

the system board

Each acts as temporary storage for data and instructions from the main

memory. Since the system is likely to use the same data several times, it is

faster to get it from the on-chip level-one cache than from the main memory.

The level-two cache memory, when fitted, has a 32-byte line size (a line is an

area of memory of a fixed size). It is controlled by the PL/PCI bridge chip

(SB82437FX). A single HP cache memory module consists of 256 KB of

direct mapped, synchronous or asynchronous, static random access memory

(SRAM). The synchronous cache memory module achieves 10% better

performance than the asynchronous module.

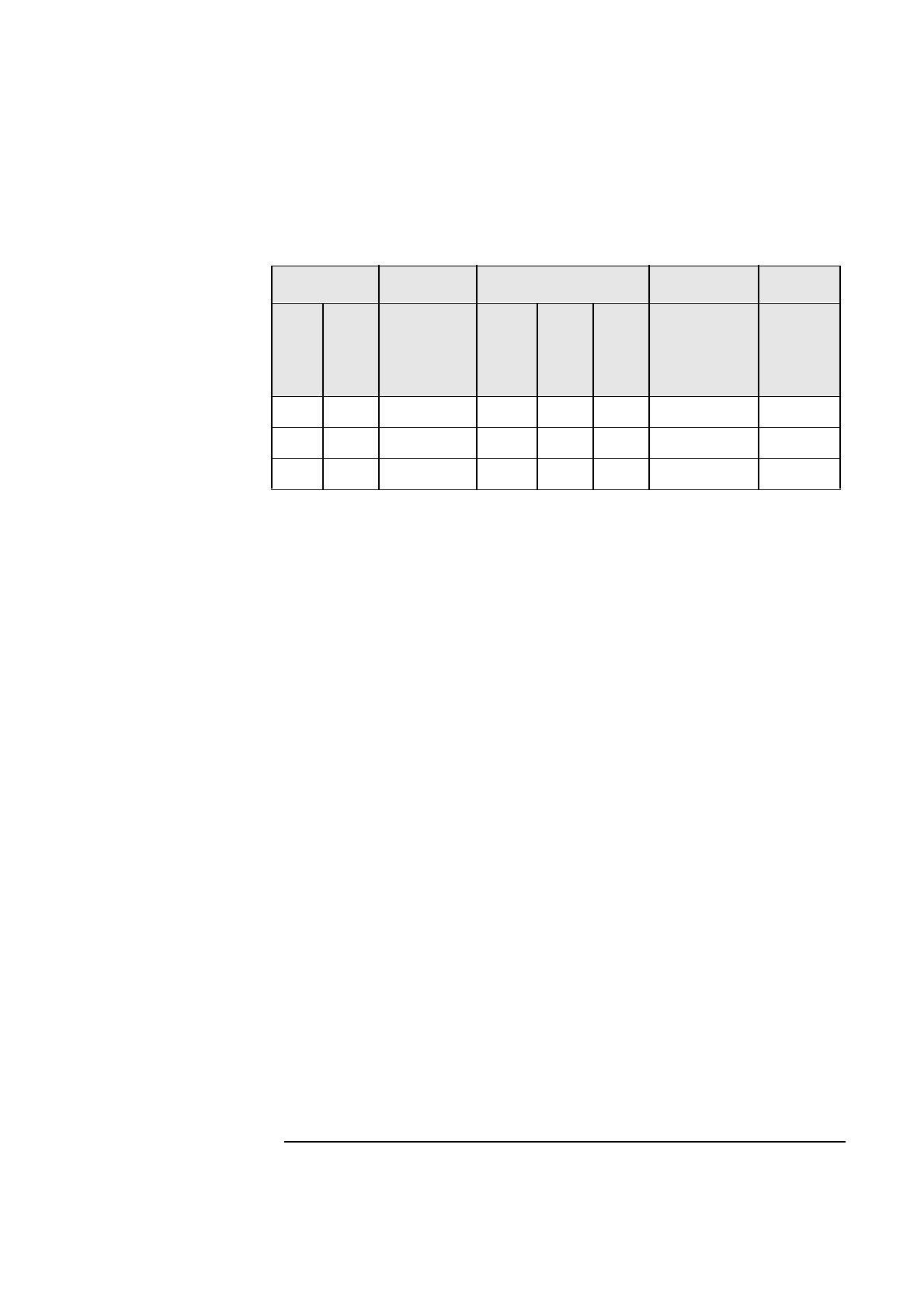

1 2

Processor-

Local Bus

Frequency

3 4 7

Frequency

Ratio

(Processor:

Local Bus)

Processor

Frequency

Open Closed 66 MHz Closed Closed Closed 2.5 166 MHz

Closed Open 60 MHz Open Closed Closed 3.0 180 MHz

Open Closed 66 MHz Open Closed Closed 3.0 200 MHz

Switch Switch

- Hardware and BIOS 1

- Technical Reference Manual 1

- Conventions 4

- Bibliography 4

- Contents 5

- 5 Video Controllers 11

- HP Vectra 500 Series 13

- System Overview 15

- D3657-63001 Models 16

- D3657-63001 - Desktop Models 16

- D3661-63001 Model 17

- D3661-63001 - Minitower Model 17

- System Features 17

- 1 HP Vectra 500 Series 18

- Desktop and Minitower Models 19

- Principal Features 20

- ≤ 40 dBA, Lp ≤ 34 dBA 21

- Power Consumption 23

- Rear Panel Connectors 24

- CD-ROM Drive Specifications 25

- System Board - (SiS Chipset) 27

- (Part Number: D4051-63001) 27

- Overview 28

- Configuration 29

- System Board Architecture 30

- System Board Physical Layout 31

- SiS Chipset 32

- Feature Summary 35

- Data Path (SiS 5512 Chip) 36

- ISA Bus Controller 37

- DMA Controller 37

- Interrupt Controller 37

- Timer/Counter 37

- SW1 Switch 38

- SW2 Switch 39

- CPU Bus Frequency Jumper 39

- Cache Jumper 40

- Memory Sockets (D4051-63001) 41

- Backplane (D4051-63001) 42

- Minitower Backplane 43

- Main Memory (UMA) 44

- Cache Memory (D4051-63001) 44

- Level-1 Cache Memory 45

- Level-2 Cache Memory 45

- Superscalar Architecture 46

- Floating Point Unit 46

- Dynamic Branch Prediction 46

- Instruction and Data Cache 46

- Data Integrity 47

- Advanced Power Management 47

- Devices on the PCI Bus 48

- Devices on the ISA Bus 52

- Feature Summary 53

- Serial/Parallel Ports 54

- Floppy Drive Controller 55

- Keyboard and Mouse Controller 55

- BIOS (version: GX.07.xx) 56

- System Board 57

- D3661-63001 Models 59

- Minitower Models 59

- Configuration Summary 59

- PCI Chipset 62

- SB82437FX-66 Feature Summary 63

- Data Path Unit (SB82438FX) 64

- Processor Socket 67

- VRM Socket 67

- Main Memory Sockets 67

- Pentium Processor 70

- Floating Point Unit (FPU) 71

- Bus Frequencies 72

- Cache Memory 73

- Main Memory 74

- Video DRAM 76

- Video Resolutions Supported 76

- Other PCI Accessory Devices 77

- Floppy Drive Controller (FDC) 79

- Real-Time Clock (RTC) 79

- Serial EEPROM 79

- System ROM 80

- Other ISA Accessory Devices 80

- HP/Phoenix BIOS Description 82

- Cannot display error messages 83

- Flash ROM may be defective 83

- Little Ben 84

- ≥ 16 MB 87

- F2=Setup 100

- ESC Exit 101

- Hard Disk 3 : None 103

- (BIOS version: GJ.07.xx) 106

- Interrupt Controllers 107

- PCI Interrupt Request Lines 108

- Video Controllers 115

- SiS 6205 Video Controller 116

- Upgrading Video Memory (UMA) 117

- 5 Video Controllers 119

- S3 Trio 64 Video Memory 121

- S3 Trio 64 Video Modes 121

- VESA Connector 126

- MGA Connectors 128

- MGA Video Memory 128

- MGA Video BIOS 131

- Further Information About MGA 131

- DB15 Connector Pinout 132

- Aztech AT3300 133

- Audio Fax/Data Modem 133

- Introduction 134

- Communications Options 135

- Configuring the firmware code 137

- 142 English 142

(1 pages)

(1 pages) (46 pages)

(46 pages)

Comments to this Manuals